Macrobizes的XM53-15P10FE20-XM53-T12.8M石英晶体单位的解释

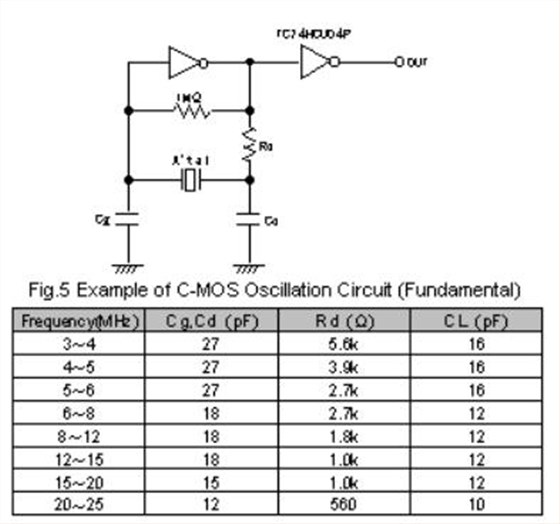

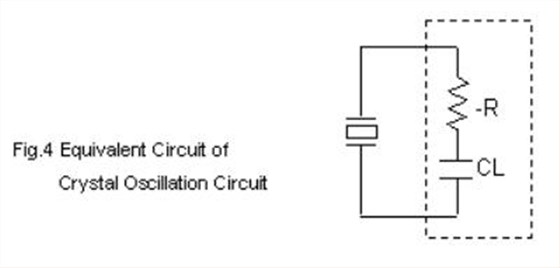

1,等效电路

晶体单元的振动实际上是机械振动。然而,如果晶体单元的行为是电转换的,则它可以用二端网络来表示。由L1、C1和R1组成的串联电路与弹性振动有关,而与串联臂并联的C0元件则是一个电容,电容由石英晶振晶体片的电介质构成。电阻R1是晶体单元在串联谐振频率下的谐振电阻。(见图1 .)

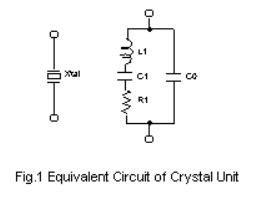

2,频率-温度

AT切割的特性目前最常用的AT切割晶体单元的频率-温度特性由三次曲线表示。(见图2)以在给定工作温度范围内获得所需频率容差的角度切割晶片。然而,实际上,由于连续过程中切割和抛光精度的结果,表观切割角可能存在一些差异。因此,有必要提高加工精度。

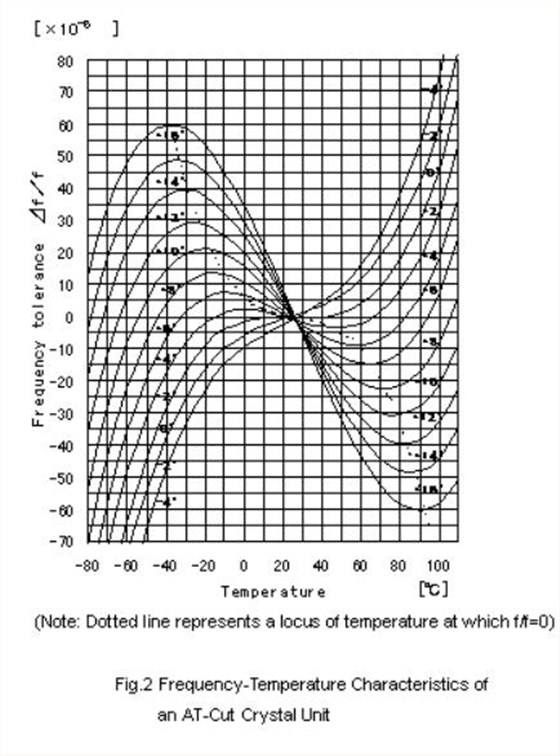

3,级驱动

由于晶体单元执行机械振动,过多的振动可能导致不稳定的振荡频率,并在最坏的情况下最终导致破坏。设计振荡电路时,应检查驱动水平,以便使用低于本公司规定水平的振荡器。图3示出了确认驾驶水平的示例方法。该方法采用电流探针来测量石英晶体振荡器电流。在这种情况下,驱动级别如下:

4,负载电容

5,晶体振荡电路的等效电路

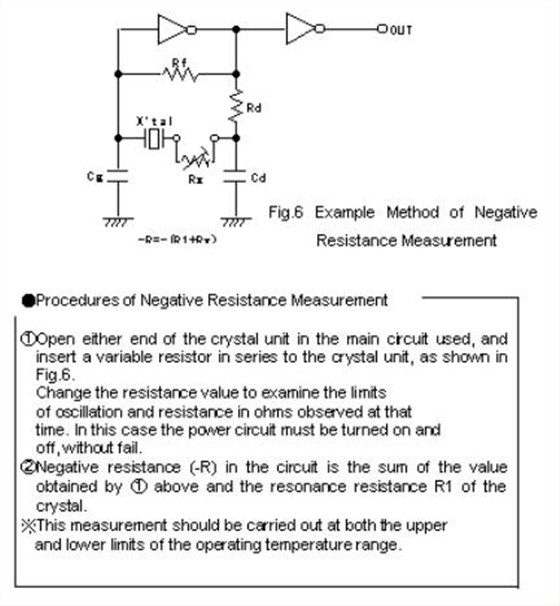

当晶体单元作为振荡电路中的感抗被激活时,贴片晶振晶体单元和振荡电路之间的关系如图4所示。为了改善振荡电路的启动条件,最好增加振荡电路的参数负电阻-R的值。如果负电阻容差不大(负电阻较小)的电路与具有较大谐振电阻的晶体单元组合在一起,启动条件会变得更糟。振荡电路应设计成负电阻值是谐振电阻的5到10倍。负载电容的中心值(用于确定振荡频率的绝对值)和可变范围(振荡频率的微调范围)也必须保持在振荡电路中的最佳值。

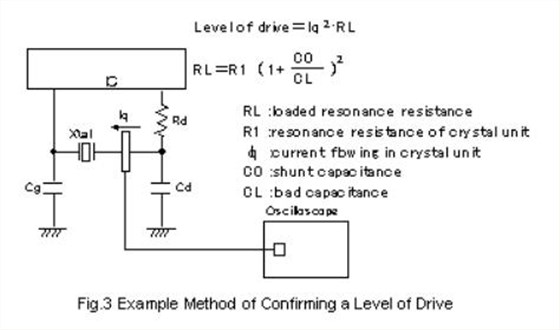

6,振荡电路

下面介绍由晶体单元组成的典型振荡电路。例如,使用的元素常数。

(1)晶体单元被设计为具有100 W及以下的较低驱动限制水平。使用前,应在实际安装电路中检查晶体电流。(参见图3 .)

必须检查电路的负电阻。根据图6可以确认负电阻。负电阻的目标是谐振电阻的5倍或更多倍。

(3)当用于C-MOS振荡电路时,电路图中的Rd是不可或缺的。(见图5)。如果连接了该Rd,驱动水平将保持在规定值内,并且可以获得稳定的振荡频率。

(4)Cg和Cd应在10?30pF。如果Cg和Cd在10pF以下或30pF以上使用,进口晶振,振荡可能很容易受到电路性能的影响,驱动电平可能会增加,或者负电阻可能会降低,从而无法保持稳定的振荡。

(5)晶体振荡电路的布局应尽可能短。应该减少电路和接地图案之间的杂散电容。应该避免晶体振荡电路图案与其他电路图案交叉。

(6)如果使用的电路、IC类型和IC制造商不同,应确认频率、驱动水平和负电阻。

*泛音振荡电路需要额外咨询

7,晶体单元应用的注意事项:

(1)当在运输或电路板安装时施加超过规定的过度冲击和振动时,晶体元件有可能断裂。当一个冲击超过规定时,一定要做特性确认,增加一个振动。

(2)超声波清洗可能导致晶体单元退化。

(3)在引线类型的情况下,将其留在引线基础上并弯曲0.5或更多。

(4)极端电路板的变形有时会导致图案脱落、端子和电极脱落、焊料裂纹。在特殊安装后分割电路板时,请小心将其安装在电路板曲线明显出现的位置。

(5)尽可能选择震动小的型号,当您使用自动装载机时,请提前确认后使用。

(6)与JC-49/U系列相比,小晶体单元(HC-49U/S、HC-49USM、UM-1、SMD)的驱动极限水平较低,为100 w及以下。因此,在使用之前,应该在实际安装电路中检查晶体电流。

必须检查电路的负电阻。根据图6,负电阻的确认是可能的,负电阻的目标约为谐振电阻的5倍。

(8)在C-MOS振荡电路中使用时,石英晶体振荡器,电路图中的Rd不可或缺(见图5)。如果该Rd达到要求,驱动水平将保持在规定值范围内,并且可以获得稳定的振荡频率。

(10)Cg和Cd应在10~30pF范围内使用,如果Cg和Cd在10pF以下或20pF以上使用,振荡很容易受到电路性能的影响,驱动水平可能会增加,或者负电阻可能会降低,从而无法保持稳定振荡。

晶体振荡电路的布局应尽可能短。

应该减少电路和接地图案之间的杂散电容。

应避免晶体振荡电路图案与其他电路图案交叉。

(11)如果使用的电路是IC类型,并且IC制造商不同,则应确认频率、驱动水平和负电阻。

一个以上的振荡电路需要额外的咨询。

TXC晶振,贴片晶振,7M晶振

TXC晶振,贴片晶振,7M晶振 TXC晶振,贴片晶振,7S晶振

TXC晶振,贴片晶振,7S晶振 TXC晶振,贴片晶振,7A晶振

TXC晶振,贴片晶振,7A晶振 微晶晶振,32.768K晶振,CM9V-T1A压电石英晶体

微晶晶振,32.768K晶振,CM9V-T1A压电石英晶体